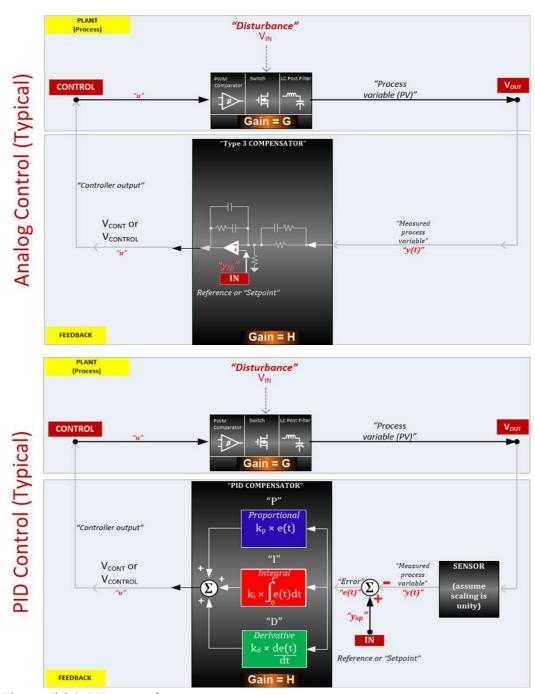

This book invokes hidden-in-plain sight Scaling Laws, discovered by Sanjaya, further popularized by Nicola, to easily design wide-input, high-power, LLC converters (hinting also at the right way to design inductive wireless power transfer systems). Also included here is the extremely tricky but powerful Dual Active Bridge (DAB), with several intimidating degrees of freedom, which engineers typically struggle with. Simple curves unveil a very simple way of designing them too. Also included is guest chapter by Nicola, on small-signal modelling, where he goes on to show how his low-level models can produce results matching Sanjaya's curves/calculations in A to Z Second Edition. In the last two chapters, Sanjaya focuses on truly understanding analog control loop theory first, then reveals an overlooked contributor to the actual step load response. He calls it the "Q-mismatch issue." He then creates a startling analogy between the impedance of a capacitor, and "PID" coefficients, to eliminate this mismatch and produce the best step load response possible, in a few easy steps.

## Power Supplies A to Z (Third)

by

Sanjaya Maniktala

and

Nicola Rosano

**ISBN:** 9798588905015 Copyright 2020: ChargEdge, Inc. (Sanjaya Maniktala)

## **Preface**

These chapters were to have been the additional pages of a previous book, to make it the third edition. Unfortunately I felt the surprisingly short-sighted publisher handed me a young arrogant (IMHO) program manager from UK, who really spoiled my mood from Day 1! I felt I knew the production process well, having written three (very well-known) books through them... I was not in the mood of "proving" my writing capability to him all over again, by providing "sample chapters" etc, by designated "Date X", "Date Y"... etc.... In fact, I already had almost all the pages presented herein written out by the first date in my contract, but the guy was just waiting endlessly only for his "sample chapter", to first kindly "approve" my writing (hopefully not technical) skills, before giving me even basic dropbox privileges to upload the very same pages presented here... Yes, they never got to see most of the material as a result, but you can now. I walked out of the contract. Publishers seem to think they "make" authors.

In my personal life, things seem to have become very difficult/busy for several reasons, so I needed to get this out to the world quickly... in particular to acknowledge Nicola Rosano... the guy who caught a string of mistakes in A to Z, Second Edition (Note: I accurately call them mistakes, not "typos"). He also did a great job in popularizing my scaling laws, first publicly revealed by me in an IEEE PELS SFBAC seminar (on youtube). But that was in pre COVID-19 times... Nicola had to do a (very well-attended) webinar instead. But the type of guy he is, he always goes out of his way to acknowledge me. He is super at that! I do that too always (e.g. my constant acknowledgements of my mentor Dr GT Murthy in India). Yes, Nicola talked about my discovery of current ripple ratio, and my discovery of "hidden-in-plain-sight" scaling laws. He also kindly provided a superb guest chapter here.

In Chapter 5 you will find another hitherto unnoticed discovery of mine, dating back to 2015. Sept 17 to be precise. I call it the "Q-mismatch" issue. See how I solved it and overnight doubled the efficacy of a vendor's vaunted programmable "PID" controllers. It was an issue apparently overlooked by all control loop experts I still feel, and my solution was just a few lines of simple calculations. Spoiler alert: I compared PID coefficients to a simple capacitor! Resulting in spectacular (200%) improvement in loop response right off the bat, over just one afternoon in San Jose.

Many thanks too, to Gregg Clark, Clyde McKay, Christina Lu, Alex Soriano, Achim Doebler, and Sridhar Vallepalli in particular, for always standing behind me! Not to forget dear Ted Tewksbury for valuable, honest insights always.

Also, Eric Wen, a very capable English to Chinese translator of some of my books, is hereby free to translate this as he wishes, perhaps with China Machine Press... I welcome that too. He was a live translator accompanying me for the whirlwind 5-city Sanjaya2016 tour of China. Always gave great inputs too. As did Sesha Panguluri, a dear friend/colleague of mine over the years, who I really enjoy thinking along with, and even relearning power all the time.... He is a master at firmware, but very adept at understanding and discussing power too. Hence his contribution to my basic way of thinking too, that I must acknowledge here finally.

With that, all I will say is enjoy the book, hope you remember me for this too. And thanks for your overwhelming support of my previous books. Over the years. My reward was: you liked it! That is all I ever cared for. Besides my two beloved Maltipoos: Munchi and Cookie.

Sanjaya Maniktala *Dec 31, 2020*

P.S. I suggest you print it out first since the figures may be all at the end of each chapter.... (sigh) if only I had the time to organize it better....! I just didn't. Also see the hints on how the entire world seems to have got it wrong in wireless power transfer (Inductive? Resonant? Ignorance!)

# Chapter 1 Resonant Power: LC to WPT

### Introduction

We will start with a rather abstract discussion before we delve into finer details. Because resonant power is tricky—to state it mildly! The devil is *not* in the details! Not initially at least. One can easily mistake the forest for the trees, getting utterly lost and not even realize it. We recommend a *soft* transition from the relative comfort of our familiar world of classical ("PWM"-based) power, into the yet-nonintuitive world of resonant power, including wireless power transfer (WPT). Preferably with a stopover at the "LLC topology", for reasons which will become clear. The ultimate aim should be to cultivate and "fine-tune" a completely new type of reasoning—to deal with something, well...*completely new*. At some point, we will realize that our prized "prior "experience", is now merely excess baggage. We need to disband it quickly. To consciously "unlearn" much of what undoubtedly served us well over the years. Because first and foremost, we need to know, that we really *don't*!

For example: "Lower the frequency to reduce switching losses and improve efficiency". Or "Minimize losses by reducing the leakage inductance". Sounds convincing! Except that neither of these statements are valid when it comes to resonant topologies, implemented "correctly" of course. In the strange new world ahead, there are almost no switching losses. And the efficiency actually worsens if we lower the frequency! Why? Because, the conduction losses, increase when the frequency is lowered, not stay fixed, as we've always tended to assume—a sort of inverse switching loss. And energy residing in the "notorious" leakage inductance too, is almost fully recoverable. In fact, it facilitates further improvement in efficiency, by crowbarring out electrostatic stored energy buried in say, EMI-suppression capacitors placed on switching nodes, and cycles them back to the input, for convenient reuse! And *no* energy whatsoever is lost "mysteriously" between the coils either. It is all accounted for. Most surprisingly perhaps, it can also be shown that *low* coupling, i.e. high leakage inductance, actually enables *greater* power, thrown over *larger* distances in wireless power transfer ("WPT"), than tightly coupled coils. Because the rectified DC voltage on the Secondary (receiver) side, tends to reflect via basic "transformer action" back onto the Primary (transmitter) side, clamping the voltage across a certain part of its coil, thereby dictating the dI/dt in it, indirectly limiting the maximum power that can be drawn by the system. So, less coupling, less clamping, more dI/dt, more power. This is a world we were totally unprepared for perhaps...!

All the above advantages however accrue only within certain definable limits. But not necessarily, "hard" limits that we are familiar or comfortable with. Nature is bounded in its own responses—to keep itself in control too! Hot air rises, to allow cold air to rush in, to cool the hot spot. Summer gives way to winter, which eventually hands us over, back once again to summer, and so on. That is nature! Self-sustaining. We need to respect its processes, and boundaries. And if we want to go further and actually exploit the awesome power that resonance in particular, brings to our doorstep, quite literally, we must also realize it comes to us with a hefty price tag attached: it demands total design expertise. Certainly, not a convincing set of alibis.... Such as, when things didn't go as planned, instead of questioning our basic assumptions, we collectively shrugged it off as "inherently poor user experience of inductive (wireless) power systems". What if it was merely poor designer experience? Undeterred, we went on to declare: "resonant systems on the other hand, have inherently good user experience". Resonant being defined as "receiver and transmitter both tuned to exactly the same frequency". Did we forget that even in our "inductive systems" we were doing exactly the same thing already? Or at least intended to do so! Actually, in either case, that "double tuning" was always an erroneous concept to start with, as we will explain. Based on some radio-frequency (RF) gut-instinct of ours from a previous life. Completely inapplicable to coupled systems such as those we are dealing with here.

It got worse: because even accepting the "resonant-inductive" dichotomy for argument's sake, one might wonder what *else* was even left to "resonate" further with, other than the receiver (Rx) and transmitter (Tx) of course, for us to announce to the world an upcoming, "resonant extension to the (inductive) Qi standard"? Wasn't that to have been AirPower, by the way? What went so "unexpectedly" wrong?

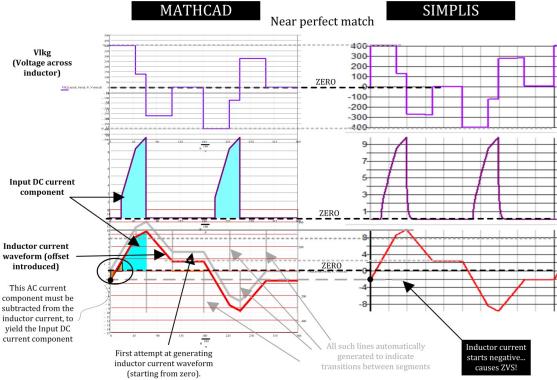

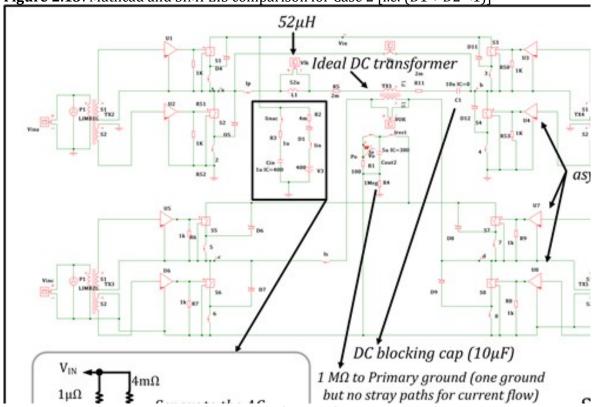

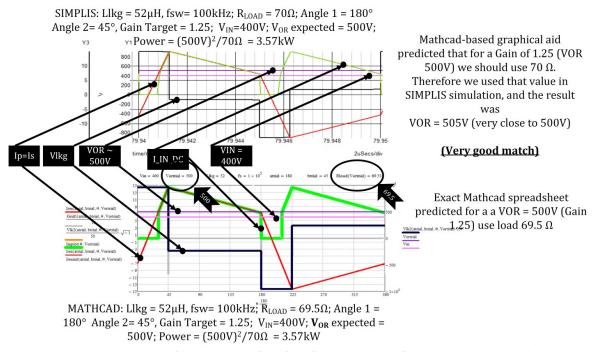

Two wrongs never made a right, certainly not three. But what really seems to have happened historically, is that engineers working in classical power conversion, or RF electronics, maybe just Bluetooth, headed into a brand new, and very tricky, area called WPT, rather unsuspectingly. And much too directly: they did not have the luxury of that fortunate chance encounter with the big brother of WPT: the LLC topology, which this author had. Otherwise, they too might have realized somewhere along the way, that if the relatively betterunderstood LLC converter today, were to be designed the same way as WPT systems of today are, there would not be a single satisfactorily working LLC converter left on the planet either. Having set our minds to really understanding resonance, preferably via the LLC converter, we should be forewarned that it can still all seem very intimidating at first. There is hope though: things can get better quickly if we follow the process of correlating our developing "mental picture" to actual simulations, based on detailed math spreadsheets, then building something however small, and finally doing sanity checks, using lab data—a process of triangulation which this author recommends, as the one he has always followed: MATHCAD →SIMPLIS  $\rightarrow$ LAB  $\rightarrow$ SIMPLIS  $\rightarrow$ MATHCAD $\rightarrow$ SIMPLIS  $\rightarrow$ LAB, and so on. Not for the faint-at-heart. Certainly not for the gung-ho.

Maybe, we will finally see a pattern emerge too! The big picture! Because acquired mastery, if any, is ultimately best measured, by how effortlessly we can communicate it back, even to the relative novice on occasion. Simplifying, what is perhaps benumbing complexity!

That may become evident in the *powerful*, *hitherto "hidden-in-plain-sight" power and frequency scaling laws* that we will reveal here. Some of those were first discovered and published in Chapter 19 of the book, Switching Power Supply Design and Optimization, Second Edition edition, by McGraw-Hill, in 2014. In this chapter we will go further: we will add to those laws, and then *exploit them unabashedly*—to unveil an astonishingly simple, *barely half-page design process*. But one that is as thorough as can be. And it can be used right away for designing *any* LLC-type resonant converter or WPT system: any power, any frequency, any output voltage, any input voltage, in fact tolerant to *input variations* too. Oh, we forgot to mention: any coupling too!

A varying input voltage, incidentally, was supposed to be the bane, if not death-knell, of LLC/resonant converters. Not so anymore, we will be pleased to discover. No longer do LLC converters have to remain fearfully confined to that familiar, comfortable location just *after* a power factor correction (PFC) stage. From now on, LLC can be front-end, (and center-stage too!). And we will also be able to, design WPT systems—*correctly* for a change.

As a sneak peek, here are the scaling patterns that we will be using (bullet "c" below, being the brand-new member of our scaling family):

- a) To double the power, halve the inductance and double the capacitance

- b) To double the frequency, halve the inductance and halve the capacitance

- c) To quadruple the power, double the input voltage

Instead of "double" or "halve", we can use other scaling factors to generalize quite obviously. The trend is obvious.

So, basically, in a few simple steps, none even involving the non-intuitive  $j=\sqrt{(-1)}$  for a change (!), we can scale an almost randomly chosen, but previously carefully-studied "kernel", to virtually any power level and frequency range we want! That is the true power of scaling, in movies, called "cutting to the chase"! And though it looks too good to be true at times, it has a happy ending: it is as accurate as can be. As can be confirmed very easily by an actual build. It is important to keep in mind that if we change the power, we do not change the frequencies involved, since those depend on the product of L and C, and we divided L by the power scaling factor and also multiplied C by the same factor, so the LC product remains unchanged. Similarly when we scale frequency, we divide both L and C by the same frequency scaling factor, keeping the ratio C/L unchanged, and that is what power depends on. So the real beauty of the first two scaling laws is that they are "orthogonal". They don't interfere with each other. That is why this discovery is so fundamental and powerful.

## **Resonance Lessons back to Classical Power**

And, though we usually recommend, not to believe anything that you may have read in Switching Power Supplies A to Z, Second Edition for example, resonance being a new frontier, the above scaling laws apply equally well to classical power.

Take a Buck, working well at 5V, 1A @ 100kHz. Keeping everything else the same, if your Boss asks you to double the power overnight, to 5V, 2A, you need to simply double the output capacitor (to keep the same output ripple, as that is proportional to load current, but inversely proportional to capacitance), and halve the inductance. Of course, though you halve the inductance, its size doubles, since size depends on ½ LI<sup>2</sup>, and current has doubled too. Similarly, the size of a capacitor depends on  $\frac{1}{2}$  CV<sup>2</sup>. Here, voltages were kept constant, so size of the capacitor will double. Size scales linearly with power, as we intuitively expected! The 5V, 2A converter will not be unstable either, because the crossover response depends on the LC break frequency (plant), which has not changed. Note also, that the current ripple ratio, r, remains the same, since  $\Delta I$  has doubled in the inductor as we doubled I, since we halved L. It all fits well! We have the same current ripple ratio so the design is still optimum. Similarly, if your Boss now demands you take the 5V, 2A @100kHz converter overnight to 200kHz, all you need to do is halve both the inductance (and size) of the L and C. In doing so, the LC break frequency which depends on the square root of LC, will also double, exactly how we want it to behave as a function of switching frequency. So, we will likely still be stable, but may need to scale the capacitances involved in the compensation circuitry. Indeed, we can just halve all of them, and things should be fine. Current ripple ratio has also remained the same here.

## WPT is (or should have been) the LLC

Any perceived, or "physical", difference, between an LLC converter and a WPT system, is not what may seem "obvious" to our naked eye—such as the distance we are throwing, or transmitting, energy across, or in the shape of the windings/coils used. "Coil" or "winding", whatever we may call it, irrespective of how it looks, just becomes an "L" in our final electrical schematic. Similarly, distance or separation, whether mm or a few meters, just ends up as a different coupling coefficient ("K") in our math spreadsheet. LLC and WPT are really not much different, *electrically*.

The biggest difference between the two is actually the scariest one! The one you "see" but don't *observe*. Or "know" but don't comprehend. In an LLC transformer, the windings are fixed relative to each other (i.e. a constant coupling), but in a WPT system, the coupling coefficient ("K"), can change dramatically with varying placement, or different alignments, of the receiver (Rx) and transmitter (Tx) coils with respect to each other. The constantly varying K changes *everything*. The overall result is hard to predict! But it can be. In fact, it has not only been fully predicted, but solved and harnessed too. Those are however proprietary solutions which cannot be revealed. But a lot of hints will emerge as we slowly unravel the grand resonant puzzle, using the simple, graphical aids presented herein.

## **Design Goals**

The graphical procedure we present, throws light on what was considered to be the most baffling piece of the resonant puzzle: what is the correct, or most optimal L-C component selection—to handle a certain power, over a desired input range? You would think that others in the field of resonant power would be very happy to know what those values are. Not really, because they likely don't even realize this is in fact the biggest challenge in resonant power. Because in classical power, "power capability" of the inductor was not the basic, overwhelming concern ever, for a designer. A simple buck regulator for example, has the simple "DC transfer function"  $V_0 = D \times V_{IN}$ . It is implicitly load independent, at least in the first order. We can draw any load current theoretically! It is essentially "current unlimited"! And we could use almost any inductance too (on paper), and that simple equation was essentially still valid. No obvious "power capability" limits. If any, they were determined by parasitics. Indeed, in practice, there is a power limit, but mainly determined by second-order effects. Such as those arising from parasitics, like DC resistance of the inductor ("DCR"), current capability of the switch, its set "safe" current limit, the current at which the inductor may saturate, or get too hot, and so on.

But all that changes dramatically in resonant power, and you may never even realize it. The current Qi standard has approved a wide range of L's and C's, without a thought. All for the same target power level Yes, they "work", sort of, but were the component selections optimal? A hint here: every LC resonant curve has a certain inherent "bulge" or "peaking" in relationship to the R present. So, you might think you have a certain gain available, but the moment you change R, and try to draw more power, the shape suddenly shapes. Try walking across a carpet that sags as you walk over it, or even is moved sideways. We will see that the gain curve we thought we had, not only "flattens", essentially preventing us from drawing more and more power, but also shifts sideways, quite dramatically in some cases, not only making our targeted power possibly out of reach, but throwing any proposed control loop in doubt too....we may have thought that to increase power we need to lower the frequency, but now since the peak may have shifted to the "other side", now we may have to reverse our entire "direction of correction", or "DoC"....without realizing it, leave aside knowing how to do it. Basically, resonance and the awesome power it brings to us, is inherently self-limiting. That is what makes all the powerful forces of nature, stay bounded and self-sustaining. A hint to our strategy to handle input droops too: to handle a definable droop in the input voltage, we need to *overdesign* the peak power capability at the maximum input voltage point! A bit more of a "bulge" But only a certain *definable* amount—to avoid straying into full-blown overdesign territory, which will impact cost and efficiency. Careful overdesign is our goal here.

The graphical aids not only point to the correct selection of the L-C components, but the best operating points too: *to do a meaningful "worst-case" system-level simulation*—for computing RMS currents, and so on. Because one of the biggest, unsaid problems facing all the simulation-fans out there, is that in resonant power, it is sadly no longer as simple as:—do the "min-load", "max-load", "min-Vin" and "max-Vin" corners! That was just child's play! In resonance, we are at the doorstep of an almost infinite array of possibilities to investigate. Can't be done without infinite simulation time! So, we desperately need to know precisely, *beforehand*, the best L-C values to use, and even the target operating frequency to set! At least somewhere very close to it—in the ball-park. By providing those in this chapter, we will finally be enabling meaningful, quick simulations too.

Simulations are in fact strongly recommended in resonant power for another reason. Because as we will see, all closed form equations in literature, base themselves on something called the "first harmonic approximation" ("FHA"). You may ask: how approximate? Hmmm, that depends! So, it is not an exact science, is it? Well, it is tricky, as we had warned! In this chapter therefore, we will focus not on creating accurate or impressive "equations", but more on unearthing the trends and pitfalls of resonance, thereby homing in on the best points for conducting actual simulations, so as to provide accurate reliable numerical estimates eventually, not approximations based on FHA. That should eventually lead to a more reliable product, designed in a predictable time-frame!

But a warning here: a lot of engineers likely did not understand WPT because they inadvertently used a certain *default transformer model* that is provided in most electrical simulator packages—which actually does *not* apply! It is based on certain assumptions which, in effect, do not correctly model either the LLC or WPT magnetic structures. So, we need to create our own simplified (transformer) model. The correct/best models can become really complex, and we'll reserve that discussion for a different day!

## The Control Loop

After selection of the power components, we inevitably land up at another fundamental juncture: *the control loop*. Briefly: how do we change our operating point to control the output? Whether it is based on changing the switching frequency, or duty cycle, phase, or set input voltage (all being "traditionally" attempted nowadays). How do we get to the best, most optimal, *highest-efficiency* point, for any coupling, any load, and hopefully for a widely varying input too. Mission Impossible? Almost! Such questions typically lead to unpredictably long, trial-and-error design phases followed by rather clumsy solutions, even from major companies trying to "spearhead" resonant topologies. The truth is: *none* of the above control methods suffice *on their own*. You need *multiple* control loops working simultaneously, yet not "fighting" each other. However, now we are once again approaching the gates of proprietary solutions, which we need to steer clear of in this chapter.

But first things first: do we even understand "L" and "C", and their basic combinations? Probably not, or we would have known long ago why resonant circuits *inherently offer such high efficiencies*. Our relentless gut instinct warned against "inherent inefficiency arising from high leakage inductance (a.k.a. low coupling)". The reality being: we can easily get typical efficiency of over 90% from an LLC converter, and that can go up close to 98% if we use synchronous rectification. Oh really?! *Despite* the high leakage? No, probably *because* of it!

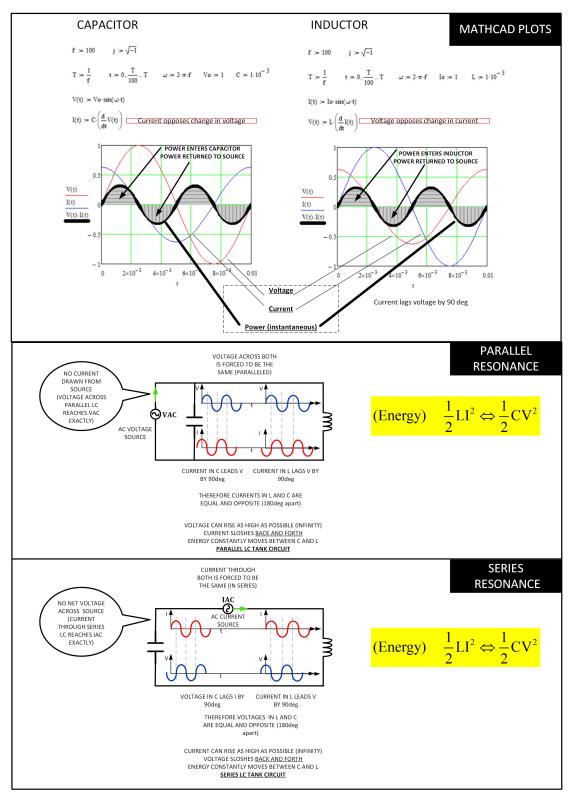

## Resonant Circuits/High Efficiency

As a quick re-introduction, or refresher, to mundane "reactive components", inductance L and capacitance C, refer to Figure 1.1. Note the essentials here: the response to any (sine-wave) harmonic of any arbitrary applied disturbance means that, for example, in an inductor, the current lags the voltage by 90 degrees; and in a capacitor, it leads the voltage by the same amount. So, calculating the instantaneous power (i.e. V×I product) over a full cycle, for both L and C (considered *independently* connected to respective AC sources for now), we learn that both of them will return *all* their energy back to their source (twice every cycle too, see the shaded portions). We conclude that pure reactive components store, *but never dissipate* (i.e. lose) energy, except within their *resistive* parasitics, such as equivalent series resistance (ESR) in capacitors, or DC resistance (DCR) in inductors. Further, parasitics may not be explicitly shown in simple schematics, but are *essential* to natural processes. So, if we discover that something doesn't converge in simulations, or "explodes" in a math spreadsheet (divide by zero, for example), let us not ignore it. Most likely it really is incorrect/unnatural. And we need to fix it.

To create a standalone reservoir of energy, or a "tank" circuit quite literally, we exploit the fact that the two lossless candidates, L and C, are essentially of *opposite types*! Like holes and electrons. Male and female! They pair well! They are complementary. So, if they are combined in parallel for example, we are in effect forcing the voltage across them to be equal always. But their currents are "90 + 90 = 180 degrees apart", which simply means that when current is coming *out of*, say L, it is going *into* C at that very moment. And so on. Back and forth! In effect, the entire parallel LC network can present an *infinite* impedance to the applied AC voltage source, because the net voltage across the LC can equal the applied AC voltage instantaneously, and eventually, the LC network will draw zero current (there is no voltage differential left to drive any current!)—which implies infinite impedance of the LC network! When (and if) that happens, the LC will contain a fixed amount of stored energy always, constantly sloshing back and forth between the L and the C:

$$\frac{1}{2}LI^2 \Leftrightarrow \frac{1}{2}CV^2$$

The sloshing occurs only at a certain natural frequency though—something that is not so obvious from the figure perhaps! But look more closely: if we want the two opposite current components (the "180 degree apart" components) in the L and C to also be equal in magnitude, for complete matching, in effect we want their impedances  $(2\pi f \times L)$  and  $1/(2\pi f \times C)$  to be equal. And that implies the applied frequency be exactly  $1/(2\pi\sqrt{(LC)})$ , called the "resonant frequency", to ensure a complete "match". A perfect couple! You can now leave them alone… A parallel LC tank it is!

When that exact matching occurs, say by sweeping the applied frequency of the source, the currents in the L and C will be not only be opposite in direction, but numerically equal too, and will thus be continuous (to each other), self-contained and self-sustaining. In this condition, no net current will theoretically *ever* need to be drawn from the input source, at least *eventually*. The voltage on the LC combination can, and will, rise to any voltage level equal to that of the source, including up to infinity if the source is up to it! But finally, the net current drawn from the source will always (eventually) be zero, provided the source is exactly at the specific "resonant frequency" above (otherwise not)! And finally, since no current is drawn from the source anymore, even if we remove it altogether, the resonant tank can go on forever, sloshing energy back and forth between the L and the C (at its natural resonant frequency). As a corollary: the only reason the voltage across the tank (and the current through it) decay, is due to resistances: ESR, DCR, and any "load resistor" that we may connect across it. Similarly, a series LC combination presents zero impedance, which is why, to avoid infinite currents, we prefer to explain it using a *current* source. Eventually, the net *voltage* across the combined series-LC will drop to zero (equal to the final voltage across the AC current source). The currents in the L and C have been forced to be the same as they are in series, but their voltage components are now opposite. In fact, those can be made exactly equal in magnitude too, but again, only at the specific applied frequency of  $1/(2\pi\sqrt{(LC)})$ . We thus have a series-LC tank!

Hypothetically, we can suddenly switch out (i.e. bypass), the current source, leaving the series LC components connected in series. Things will carry on as before! Thinking harder, we realize we have arrived at exactly the same configuration as the parallel LC tank if its voltage source were suddenly removed! Both are merely a simple loop consisting of L and C now, with circulating currents accompanied by pulsating/alternating voltages, with energy constantly sloshing between the L and the C, and with *no* dissipation ever. The only difference being that in one case we used a voltage source initially, to set the remnant voltage amplitude across each component of the now standalone LC tank, allowing the current to be what it is (based on impedances), and in the other case we used a current source to set the remnant current amplitude flowing in each of the L and C, but allowing the voltage across each to be what it is. In both cases however, we can think of it in the following way too: similar to the topmost Mathcad-based plots in **Figure 1.1**, the inductor "returns" energy to the capacitor (which is now behaving as the applied AC voltage source!). A bit later, the capacitor "returns" its energy back to the inductor (which is now behaving as the applied AC current source). Notice how it is all so complementary and elegant!

Note also that in the process, we can get huge "amplification" too: for example, if we had connected the series LC tank with a voltage source in series instead of a current source, we would get (close to) *infinite* currents. Similarly, a current source applied to the parallel LC would have forced it to infinite voltage.

Intuitively, in a series-LC circuit at resonance for example, the L and C impedances are equal and opposite, so it behaves quite like a "dead short" at that specific "resonant" frequency. This resonance action is basically very helpful to be able to create fields extending over greater distances, to instigate Faraday's Law, which is what we try to do all the time in WPT. That was exactly how Nikola Tesla was also trying to do it. He created very high voltages (millions of volts), instigated by a huge dV/dt spike, produced by interrupting very high current flowing in a huge inductor (V = LdI/dt of course).

But note how nature tends to self-stabilize: the more energy you try to draw from the resonant tank, the less effective it becomes, because it "knows" that now you have introduced (load) resistance, and the resonant voltage/current starts collapsing. Like a carpet pulled from under your very feet as you try to walk across. But it is not that bad: without resonance, energy wouldn't have even made it over that distance to start with! That is why it is so important to characterize the actual resonant response. How it changes! A big part of that natural response, in effect the inherent "power capability" of an L-C combination, is determined by the ratio of the resistance (i.e. the applied load mainly) and the ratio  $\sqrt{(C/L)}$ . This simple fact actually leads to one of the scaling laws which will be discussed in more detail later.

## **Resonant Circuits and Efficiency Nuances**

It is clear: any inductance present in a circuit, discrete or "leakage", is nevertheless still just an "L" in the circuit, and it *will* attempt to return all its energy back to the source. It can't ever dissipate! Not within itself for sure. Maybe in external resistances! If present. And further, in combination with a nearby C, it can also form either a deliberate, or an inadvertent, tank circuit, constantly exchanging energy between the two. Because neither can dissipate! This is essentially why resonant circuits are inherently so efficient to start with.

Generally, if we focus on just reducing ESR, DCR, RDS etc., we will get very high efficiencies. Quite automatically! Yes, instead of AC sources, when we introduce switches connected to DC voltage sources to push energy in at a certain rate, maybe with the intention of controlling the output voltage by choosing the switching frequency, either to be close to, or far away from the natural "resonant frequency", we do have to consider the possibility of *switching losses*. Because we will be turning our switches ON and OFF quite fast, simply to minimize crossover dissipation inside them! *But how "fast" is good enough*? Resonance is actually very forgiving in this regard too. Because it can be shown, as an example, that if we are using the popular half-bridge or full-bridge topologies, we can actually use the leakage inductance present, to coax "soft-switching", or "zero-voltage switching" (ZVS), thus reducing switching losses dramatically. Leaving us with only conduction losses, such as those from the DCR of the windings, or coils, to contend with, and minimize. No need typically, for "state of the art" wide band gap (WBG) switches such as Gallium Nitride (GaN) or Silicon Carbide (SiC). Cheap, low-voltage Mosfets, albeit with sloppy switching characteristics, *but with low RDS to reduce conduction losses*, is the way to go in most resonant converter applications.

Keep in mind though, as another indication of the self-stabilizing, self-limiting advantages of natural resonance, it can be shown that as we lower the coupling, though that enables *greater* power delivery, it also comes at an increasing cost! The dominant circulating/excitation current component (the unused energy returning back to the source every cycle), can become rather high, leading to *higher conduction losses*, thus necessitating closer and closer attention to heat dissipation. And to thermal management. Eventually however, the dissipation term mentioned above is the specific one which ultimately impacts, and dictates, the efficiency of any resonant converter, *provided of course, ZVS is being ensured*.

The correct region to head to, for enabling ZVS, is indicated in **Figure 1.2** using a representative resonant curve. It can be shown that ZVS is possible only if you switch to the right of a (presumably single) resonant peak...on the left side of that peak, you get hardswitching, which is essentially lossy and gives out a lot of EMI too. Basically, to the right of any resonant peak, the LC network appears "inductive" (on the left it appears "capacitive"). We do remember that inductors "complain" whenever we try to suddenly interrupt current flowing in them—the very reason we need a catch diode in "square"/PWM topologies, as was explained in Chapter 1 of Switching Power Supplies, A to Z, Second Edition, published by Elsevier in 2012. As a result, inductances tend to maintain/force current continuity, searching for whatever path may be available to continue to push current through. So, in a typical halfbridge (totem pole), if we switch OFF the lower switch (Mosfet), the current in the "inductive" LC network being switched, will tend to freewheel—through the body diode of the upper switch, the only available path! We then just need to leave a deadtime of typically 100-200 ns before turning the top Mosfet ON. Because during that tiny deadtime duration, the voltage across the upper Mosfet will be forced to near-zero value, by the "inductive" network: its body diode will be forced into conduction to maintain current continuity. And so, when we finally turn the upper Mosfet ON (after the deadtime elapses), we get lossless, or zero-voltage switching (i.e. with no overlapping V-I crossover, since V was almost zero during the entire switch crossover).

Surprisingly, none of the WPT practitioners out there seem to have understood this aspect either. Especially those who try to control the output very simplistically: by trying to vary duty cycle, or phase or even the input DC voltage applied to the transmitter, keeping frequency fixed. All these were inspired by classical PWM power conversion obviously, where fixed-frequency techniques are preferred *for reducing EMI* in particular. They didn't seem to realize that with the typical natural *frequency shift* of the resonant peak to a higher level when you load it, as we will explain, they could easily land up, *without doing a thing*, on the wrong (left) side of the peak—where ZVS is no longer possible. Now we will get high losses and much higher EMI too! Just the opposite of what we were intending.

Energy is also not "automatically lost" between the receiver and transmitter coils, as some think. There is no "resistor" present in that space, for dissipation to occur! Keep in mind that no part of any energy balance-sheet is ever "un-accountable", especially not when we are in the near-field region, as explained further below. Energy is lost only in resistances (as heat), including in the DCR of the coils themselves, but not in the airspace between! Unless of course there is a metal object present therein (the "foreign object detection (FOD)" issue), which generates eddy currents and thus heat. But that too is still, in effect, just a resistance, an identifiable/quantifiable one, in the overall effective electrical schematic. It can all be accounted for. There is no black magic, nor black holes involved here!

It is however always helpful to mentally distinguish between *fields* and *waves*! Waves indeed, we may not be able to keep track of fully! They tend to disappear into outer space. Efficiency truly becomes questionable. But for fields, those restricted to the "near field" region, it is just all *stored* energy! *Fully deliverable, with the rest being fully recoverable!* None of it is ever inherently doomed or "missing". And luckily, this near-field region extends up to 480 meters for our typical 100kHz operation (it is precisely 0.16 times the wavelength, which is 3 kilometers in our case)! So, we can certainly disregard electromagnetic waves, which will appear only when, hypothetically, the 100kHz fields we generate are strong enough to reach into the far-field region, i.e. half a kilometer away! Which they clearly don't! Why? Because Nikola Tesla is not around anymore! Yes, he had tried all that! And nowadays, instead, we have UL (Underwriters Laboratories) and FCC (Federal Communications Commission) watching over us carefully! Quite a sobering thought!

Things will change dramatically only when we take our frequencies up to RF-levels. Indeed, RF-based WPT methods do have intrinsically low efficiencies, of around 5-10 %, because at their typical 2.4GHz, the near field region ends at 15mm! Less than a third of a finger away! As a result, a huge fraction of the energy those RF-technologies create, do leave forever as electromagnetic waves headed for distant planets. But not so in any of the near-field, lowfrequency category of resonant topologies under discussion here. The underlying physics of resonance is shared by all the LLC/WPT methods that we are discussing here. These clarifications, combined with the basic properties of inductors and capacitors, imply that on paper at least, any resonant system can approach the ideal of 100%. Provided it is correctly designed, as was hinted at in our ZVS discussion too. Usually, we just stop pushing efficiency at the point where it stops making economic sense. A product needs to be costeffective after all! The ostensibly "fundamental" question of some: "What exactly is your efficiency", has a simple answer: "How much do you want?" Actual implementations of nearfield WPT should certainly be questioned. To know for example, whether they are exploiting ZVS or not. That will affect efficiency. And distinguish technologies. But nothing arcane though.

## **Control Loop or not**

As indicated, resonance is powerful, but inherently self-limiting too! Which is why it is very tricky to design in. The peak bulges, but then collapses as mentioned! Nothing obvious we can carry over from classical power for sure. That was all relatively "single-direction" and predictable.

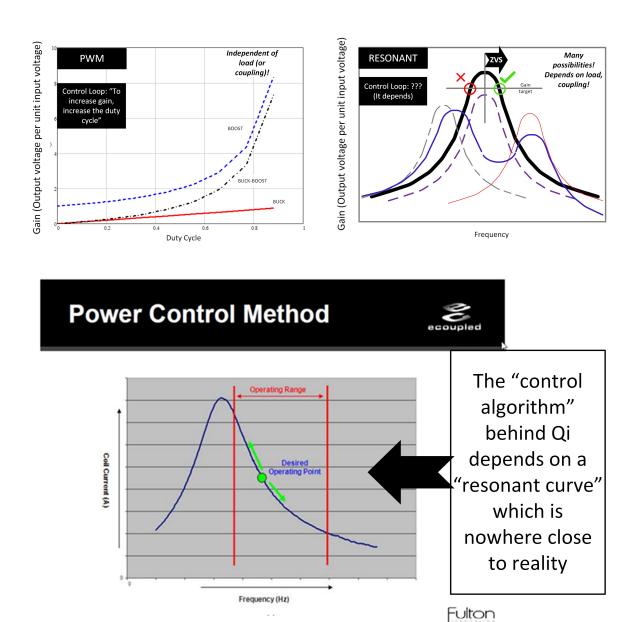

We realize that in a simple buck regulator we didn't even need a control loop per se. For example, if we had 15V input, and we wanted 5V out, we just had to drive the buck converter at one-third duty cycle, *irrespective of load current, and we would always get 5V* (though indeed, the load must be reasonably high to enforce continuous conduction mode "CCM"). At a later design stage, when we finally introduced the (AC) control loop, its purpose was only to impart much higher *precision* (regulation) to the desired/set output voltage.

The "direction of correction" ("DoC") was unconditionally obvious too, as in all of classical power: for all three fundamental topologies, you just need to increase D, and in response,  $V_0$  (or the DC "gain" which is just  $V_0/V_{IN}$ ), would definitely increase. No mystery there. See **Figure 1.2**. But coming to resonant circuits where traditionally, "frequency modulation" is used to control the gain and thus the output, we should actually *not* be making any of the three implicit assumptions made via the familiar "control algorithm" reproduced in **Figure 1.2**, from Fulton Innovation (an Amway subsidiary, the guys who actually created the first versions of Qi).

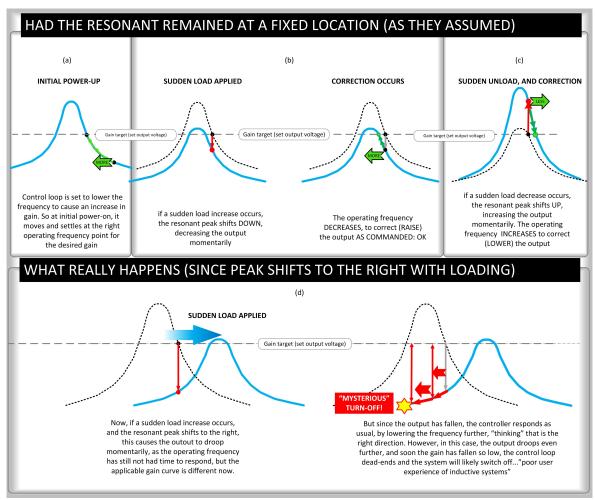

- a) The height of the resonant curve is *not* fixed as it seems to be, from their diagram: it is in reality, a strong function of load. It will inevitably start *flattening out* if you try to increase the gain to deliver more power to the load (by lowering the frequency). That flattening, indicative of the self-stabilizing properties of resonance, was clearly not considered, or anticipated, in the Fulton/Qi curve. But the mistake is not fatal! It could still be considered implicit therein and in fact, even if that happened, it would likely be handled quite well by any simple control loop, with a fixed DoC, as indicated by the load transition cases shown in **Figure 1.3** (a to c). But in fact, that was not even close to the actual shape of the resonant curve they had on hand, as we will reveal!

- b) The resonant curve is also *not fixed* relative to frequency, as the curve from Fulton implies. It can move *sideways*. *To the right for higher loads*. And not just slightly, but dramatically, as we will learn. Precisely 41% for very high loading and a coupling of 0.5, as an example! It is a complicated function of both load and coupling in general.

**Note:** This sideways shift of the peak is not even obvious in simulations if we use the built-in default "transformer" available in most commercial simulator packages.

Now, with the lateral shift of the resonant peak, strange new things will happen! Qi for example assumes the peak is fixed and thus lays out a lower limit of 115kHz (to avoid rolling over it!). But what if the peak was actually at 130kHz? Now, if we headed towards 115kHz, we could also easily "roll over" the top of the (flattened), shifted peak, especially if our C/L ratio was inadequate, in relationship to the R (load resistor), i.e. insufficient power available from the resonant circuit to meet our basic power requirement.

There is in fact something almost intangible, called the "power capability of a resonant circuit", which depends on C/L as previously mentioned. Unknowingly, Qi "approved" many transmitter coils with widely-varying, almost random, C/L ratios, all supposedly for the same 5W/15W power level (and often for the same  $V_{IN}$  too). The overall power capability of the selected reactive components was all over the place! They were probably thinking "Buck" when they wrote their standard, which as we indicated has a transfer function independent of power (in the first order). But resonance is very different.

Worse, by the flattening and roll-over, you would then land up in the region to the *left* of the peak, *where your entire DoC needs now to be reversed*: here you need to *increase* frequency to deliver more power, not decrease it! But if you didn't even know that you

had rolled over (and how could you?), the power would collapse increasingly, as you lowered the frequency further and further, eventually leading to a "mysterious" turn-off—due to power inadequacy, control loop confusion, or just too low a voltage on the receiver for it to even be able to communicate back its requirements. See **Figure 1.3d** for a similar example of what can happen!

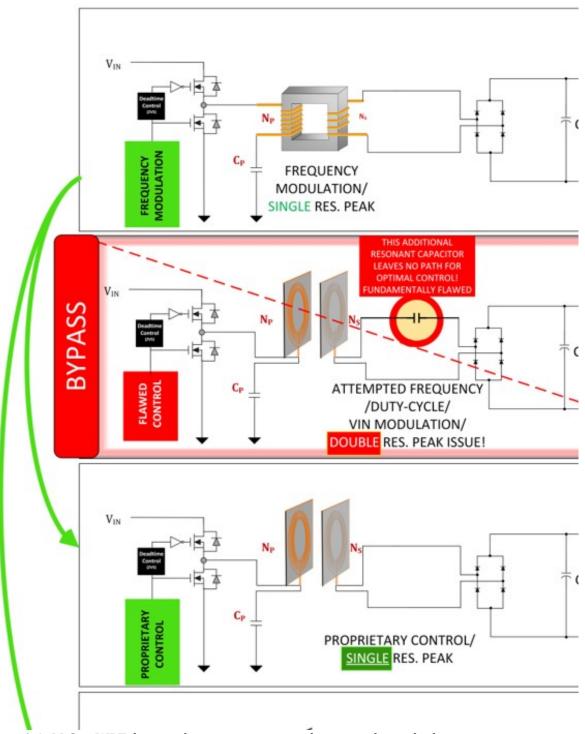

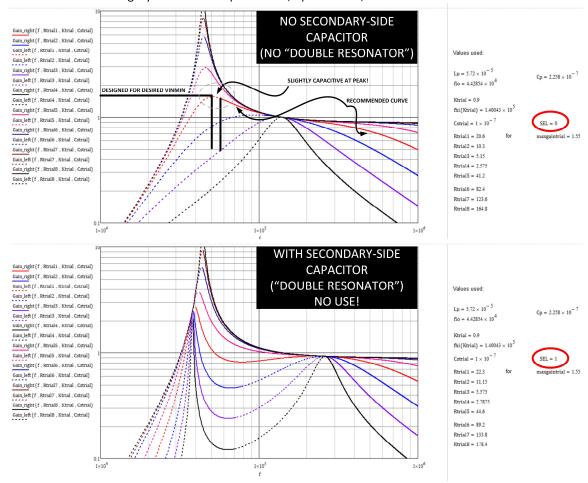

c) Finally, why assume we have just one resonant peak? There were *two* capacitors remember? One from the Primary (transmitter), and another one *expectedly reflected from the Secondary* (receiver). Both would end up interacting with the existing L. So, *two* second order poles. *Two* resonant peaks—basic physics! But looking back, *all those engaged in WPT today*, seem to have based their efforts on a *fundamentally flawed "double resonator"* assumption, which unbeknownst to them, gave not one fixed peak, as they had assumed, not one *moving* peak (which they could have conceivably handled, say by exotic or proprietary control algorithms, had they known), but *two wildly moving* peaks, *not even amenable to a simple DoC, or even a very clever control strategy*. And that is precisely how the world possibly ended up with "inherently poor user experience of inductive systems". This is the critical flaw encircled in **Figure 1.4b** too. The entire WPT world subscribes to it! They just (still) don't know, that they don't!

As mentioned, in the early stages of development of WPT, engineers with RF backgrounds likely, instinctively felt they needed to *tune the receiver to exactly the same frequency as the transmitter*, each independently measured and set, for ensuring "maximum power" transfer. Or maybe, their theory was based on some transmission-line-inspired "impedance matching" concept. Also RF! Actually, it was all just prior mental conditioning, not applicable to relatively closely-coupled, near-field systems at all, i.e. those involving fields, not waves! And by now, it may be too late to correct. Initially, they could have headed to WPT via the relatively well-understood LLC topology shown in **Figure 1.4a**. We now realize that *has only Primary-side resonance* (no "Cs") *for good reason!* We could then arrive at a better form of WPT shown in **Figure 1.4c**. After that, to improve the magnetics further, we could evolve towards **Figure 1.4d** or something similar. But unfortunately, by now, both the potential elimination of Cs as applied to the field of WPT in **Figure 1.4c**, and the magnetics of **Figure 1.4d**, are likely proprietary. A bit late in the day to play "catch-up".

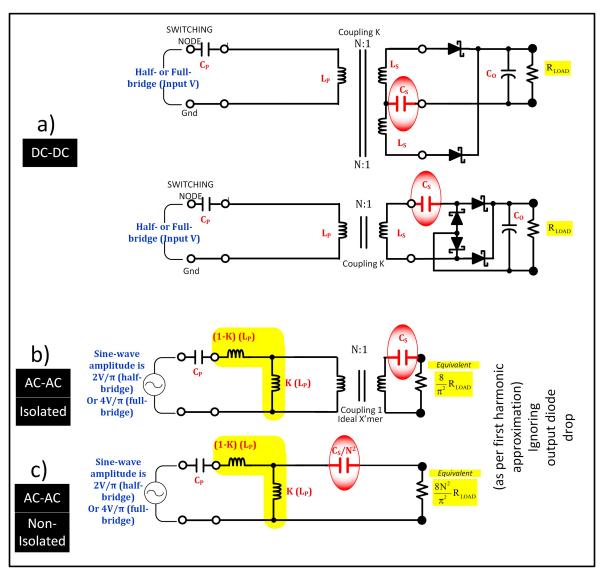

The double-resonator flaw (i.e. the presence of C<sub>S</sub> in effect), is shown encircled in the equivalent circuit diagrams presented in **Figure 1.5** too. But that figure has some new details, which will be helpful in our upcoming design calculations/procedure.

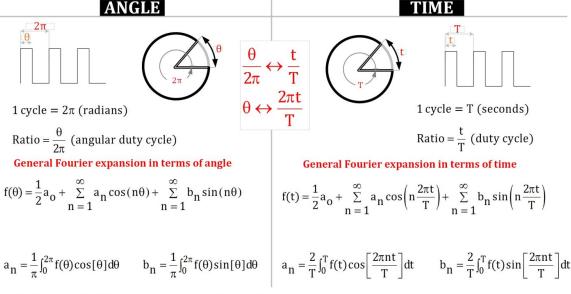

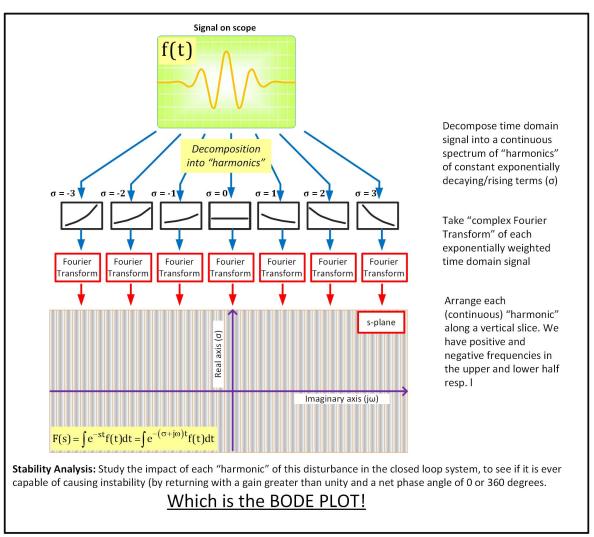

## The First Harmonic Approximation

**Figure 1.5** shows us how to go back and forth between equivalent AC and DC models, including reflecting impedances over to either side of the transformer, for enabling simple calculations. That is all based on keeping in mind that even if we apply a "square-ish" voltage shape to a general LC network, we need to mentally break it up into its Fourier (sine) components....and see the effect of each sine component on the network. Later we can reassemble the responses back. Turns out, it is usually sufficient to assume that of all the harmonic constituents of the "square-ish" waveform, only its fundamental (first) harmonic has the main, or dominating, effect. Therefore, resonant topologies are commonly studied using the First Harmonic Approximation" (FHA). We ignore other harmonics.

Using FHA, it can be shown that the peak-to-peak value of the first harmonic (sine wave component) of the input voltage, *exceeds* the peak-to-peak of the square wave responsible for it, by the simple factor of  $4/\pi=1.273$ . But in a half-bridge, as opposed to a full-bridge, we also have to understand that its resonant capacitor acquires an *average DC level of half the supply voltage*, subtracting from the effective input applied to the L-C network. So, in effect we need to halve the stated peak to peak value, down to  $2/\pi$  times  $V_{IN}$  as indicated in the figure. Using FHA, and further realizing also that if we "reflect" a given load resistor present on the output of a DC-DC converter, to an "equivalent" Primary side resistor, we must maintain the actual dissipation (energy) term even through the process of "reflection". The energy can't change by reflection! So combined with the FHA, it can be shown that a certain "R" present on the Secondary side (on its *rectified* DC output) can be reflected back to the Primary, to appear as an *effective (AC) resistor* of value  $8N^2/\pi^2$ , as shown in **Figure 1.5**.

**Note:** Keep in mind that the turns ratio used by us is " $N=N_P/N_S$ " whereas most simulator packages prefer to call turns ratio as  $N_S/N_P$ . We may have to take the reciprocal! So, the "equivalent AC load resistor" is actually of <u>smaller</u> value (in ohms) than the corresponding DC load resistor from where it came from, by the factor  $8/\pi^2 = 0.8107$ , all from FHA analysis. That equivalent AC load resistor, we can then reflect onto the Primary, as a typically larger resistor (since N > 1 typically), by the factor  $N^2$  (to keep dissipation the same too, despite reflection). Combined, we get the overall factor of  $8N^2/\pi^2$ , as indicated in **Figure 1.5**.

Similarly, maintaining the stored energy too, in the process of reflection, and realizing that voltage scales (typically increases), by a factor  $\times N$  in going from the Secondary to the Primary, and current scales (typically decreases) by the factor  $\times (1/N)$  in doing the same, a capacitor must reflect in going from the Secondary to the Primary, as  $C_S/N^2$  (its value typically *decreases* since its voltage has increased in the reflection process, but energy is fixed). Similarly, an inductor reflects (typically *increases*, since the current through it has decreased) as  $L_S \times N^2$ . All this is based on maintaining the same " $1/2(LI^2)$ " and " $(CV^2/2)$ " i.e. energy terms, in going from the Secondary to the Primary!

**Note:** That is why in classical power conversion, we strongly recommend lowering the "trace inductance" on the Secondary-side of a Flyback converter. Even the typical 20nH/inch reflects into the Primary by turns-ratio squared, becoming a rather *huge* stray inductance whose energy has to be usually just burnt (dumped) in the Zener clamp at every turn-OFF transition. We will not derive any of these formulae here, as most references on the subject usually carry all that. We will focus on gathering and using all the tools necessary for a very thorough and complete design.

Note that in **Figure 1.5**, the "tuning capacitor Cs, which as mentioned, everyone seems to have rather incomprehensibly introduced in modern WPT, reflects to the Primary and creates another resonant peak! It is a fundamental flaw, as it leads to the *double-peak* gain profile possibility hinted at in **Figure 1.2**, which as mentioned, is not even amenable to any known DoC, or any apparent/exotic control loop strategy—to ensure ZVS for example, *or even a dependable output*. And worse, all the "fixed frequency" approaches, i.e. changing phase, or input voltage, or duty cycle, are even less promising than frequency modulation methods in this regard.

## What is so special about the LLC?

As suggested, our first stop should have been the better-understood, more-familiar, LLC converter. From there, on to WPT. Because we realize that both LLC converters and WPT systems need to be designed in *much the same way*. They *are the same* topology! Or at least *should* have been, had modern WPT implementations been done right. LLC and WPT constitute two sides of the same resonant coin.

As indicated, what is so "wrong" in WPT today, and in fact totally unnecessary, and *not* there in LLC (for good reason), is the presence of the Secondary-side capacitor Cs shown in <u>Figure 1.4b</u>. This figure is exactly where *all* attempts in WPT are stuck today, without even knowing it

As also indicated, it all came about perhaps based on a wishful attempt to tune  $C_P$  and  $L_P$  in the Tx, with  $L_S$  and  $C_S$  on the receiver, *radio-frequency style*, expecting maximum power. Both  $L_P$  and  $L_S$  were in effect measured independently, forgetting the effects of their mutual interaction when brought closer. But surprisingly, everybody is doing exactly that in WPT today, though the tuning frequencies may differ.

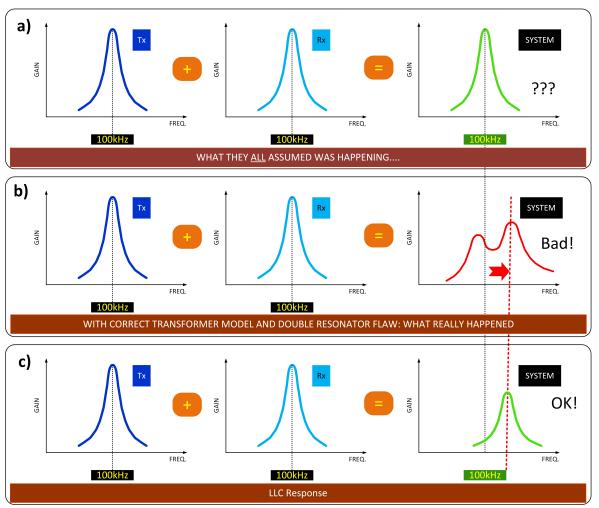

They *all* apparently assume what is now presented more clearly in **Figure 1.6a**: that if they tune the Tx to say 100kHz (as Qi does), and the Rx to the same 100kHz, *independently*, then the net resonant response when the coils are brought closer, *is still a single peak at 100kHz*. But what really happens, is also shown in the same figure, and it can be easily proven using the basic, but accurate-enough, "transformer model" shown in **Figure 1.5**. The gain profile not only shifts sideways, but splits into two virtually *unpredictable* peaks (**Figure 1.6b**) in their case.

Unpredictable in "height", just for starters (so how can you *ever predict* the "power capability" of any L-C network anymore?). Also, not only shifted sideways, but *two* shifting peaks (no bullet-proof control loop seems even possible anymore). Plus, the right of one peak is also the left of the other (so where exactly do we need to "aim" for, to get ZVS?). There are problems galore for **Figure 1.6b**.

In contrast, had we gone down the LLC path, we would arrive at **Figure 1.6c**. That recognizes and predicts both the extent of the flattening, and the lateral shifting. It has only one peak too! It is thus fully amenable to a properly-designed, smart control loop. Though of course, in WPT, to handle the variable K, we will need to progress on to proprietary control loops! That does get very, very complicated. Not to be discussed here either.

Keep it simple stupid (K.I.S.S.) as they say, but don't be stupid enough to oversimplify either! All those who did exactly that, and tried to keep a fixed switching frequency, resorting to duty-cycle, phase or  $V_{IN}$  modulation to control the output, didn't realize that they all *will* land up on the wrong side of the resonant peak (or peaks in their case) sooner or later, i.e. with or without any  $C_S$  present! So: poor "user experience" eventually? Probably worse than basic  $Q_I$  too.

## The Elusive Resonant Peak

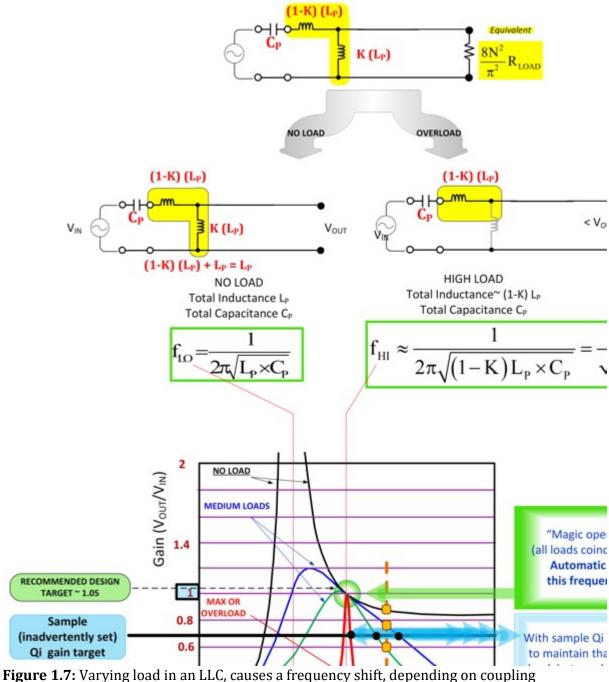

Now let's explain the lateral shifting of the (single) resonant peak using the simple "transformer model" shown in **Figure 1.5**. The Primary inductance  $L_P$  splits into a Secondary-side coupled portion " $K \times L_P$ " and a leakage or uncoupled portion  $(1-K) \times L_P$ . We are ignoring the encircled, flawed  $C_S$  now. See the equivalent circuit being carried over to **Figure 1.7**, to explain one of the key reasons why the LLC became so popular to start with, as compared to other "competing" resonant topologies such as the series-resonant converter ("SRC").

We now show in **Figure 1.7** how varying loads produce a predictable shifting of the resonant peak as indicated, *between two extremes*. One extreme occurs for no load, called " $f_{LO}$ ", the other for very high loading, called " $f_{HI}$ ". One peak location is based on the *entire* Primary inductance coming into play, the other on leakage inductance only. The gain curves for intermediate loads fall somewhere between the two operating frequency limits,  $f_{HI}$  and  $f_{LO}$ . Note that it is always a single peak in our case, but shifting between two extremes. *It is not a double peak!* No constituent curve in the set, has two "humps". Look closely.

This is what led to the big perceived advantage of the LLC. It simplified the control loop and the design of switches and all associated circuitry too (no need to go to very, very high frequencies just to reduce gain, say at very light loads, as was the situation with the "competing" SRC topology). This also leads to a rather narrow, manageable band of EMI. We could basically keep  $f_{\rm HI}$  below 150kHz, just to pass EMI testing more easily, and restrict the operation between  $f_{\rm HI}$  and  $f_{\rm LO}$ , for *all* loads.

Notice how all the gain curves intersect *exactly* at the point described by: Gain=1 and f=  $f_{HI}$ . Let us call this the "magic operating point" ("MOP"). All the curves intersect here because at this frequency, the leakage inductance and the resonant capacitor are in complete resonance, and form a "dead short" in effect as explained previously! With that "dead short, the entire input voltage will appear unfettered, straight at the output, irrespective of load! So,  $V_{IN} = V_0$ . i.e. Gain =1, for any load!

Note the eerie similarities to the "load-independent DC transfer function" of a Buck as discussed earlier! So theoretically, now, if we operate precisely at  $f_{HI}$ , we would not need to do anything at all to adjust the output, for any load from zero to maximum! Provided we had designed our circuit for a gain target of exactly 1. What that means is the set reflected output voltage (often called  $V_{OR}$  in a Flyback for example), would need to be exactly equal to the applied DC input voltage. Then, clearly:  $G_{OR}$  in =1.

Theoretically, we could then even choose to operate precisely at  $f_{HI}$  always. No control loop in place. It does seem plausible and promising too: we would be operating to the right of any applicable resonant curve always (for any load), and we would thus always get ZVS too, automatically. Since it is fixed frequency, it is good for EMI testing too! All we really have to do is to specify the *right* turns ratio so that  $N \times V_0 = V_{IN}$ . As simple as that! It should work! A perfect topology it seems! What if anything, is wrong?

Like all things "power", nothing is ever straightforward! First, this series L-C "dead-short" visualization is true only in the first-order. When we introduce parasitics, the output starts to droop at high load currents due to simple resistive voltage-divider action between the DCR of the Tx coil (RDS of FETs too), and the load resistor. So, we may opt to forcibly ensure that we have very, very low parasitics, just to make the output droop "acceptable" (whatever that means). But that will require very, very thick expensive copper! Instead, how about *using resonance* (more) effectively, to literally boost (amplify) the output voltage if it starts to droop too much? In fact, then maybe we can amplify it even further to compensate for a droop in the input too! That will be much smarter and more cost-effective, compared to using utterly thick copper windings! That is actually the right way to do it, the basic method underlying our graphical aids too. It does demand a lot of design expertise though, at least to generate those curves. But to use them is very easy, as we will learn.

In **Figure 1.7** we show the basic problem with the fixed-frequency (no control loop) method. If the set fixed frequency does not coincide *exactly* with  $f_{\rm HI}$ , and/or the desired/set gain is not exactly unity, we will land up slightly to one side of the MoP, where we can see the gain curves can drop off dramatically (under our feet, quite literally) as we change load, especially if we are to the left of the MoP. If we land up there, we would likely experience a dramatic, droop in the output, for load variations. Typical tolerances in L and C, not to mention variations in coupling (which also affects the leakage inductance, and thereby  $f_{\rm HI}$ ), will play havoc with the desired output. The only way out is to manually tune every single transmitter in production, to the exact resonant frequency of the specific L and C we happen to have on a given board (yes coupling variations included).

We conclude that the constant, fixed-frequency approach, may make a "good (tuned) demo board" to impress the uninformed with, but it doesn't promise to ever qualify as a commercial product! Not without a control loop. That approach may have "sort-of" worked with a classical power topology, as we too indicated was possible for a Buck, on the basis of its simple DC transfer function, but resonance is not to be underestimated. We do need a control loop here, and for many *more* reasons than we ever needed it in a Buck!

If we have no tolerance even for L and C variations, how can we ever handle the second most vexing problem of all: input voltage variations. The most vexing of course being the variations in K, especially in WPT systems, as we had mentioned.

The graphical technique proposed here will handle input droops too. We realize that since  $Gain = V_0/V_{IN}$ , if  $V_{IN}$  falls, then for maintaining a fixed  $V_0$ , we just need to increase the Gain by the same factor! That should be easy to accomplish, almost automatically by a control loop, say one based on frequency modulation, as is commonly used in LLC converters. Provided we have the right "bulge" in the selected resonant curve, we can simply head towards  $f_{L0}$ , stopping wherever we reach the desired output. Indeed, handling K-variability is another huge challenge altogether.

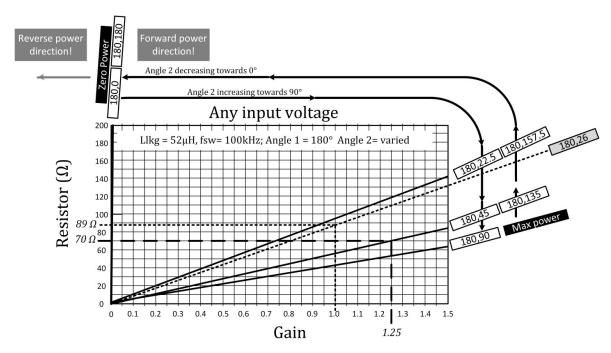

## Heading to a Practical Design: Setting Gain Target

In this chapter we are recommending that we must always, for the LLC and even for WPT, try to ensure that our system restricts its operating region to the region between  $f_{HI}$  and  $f_{LO}$ . This we can ensure by *designing it to have a "gain target" (i.e. VOR/VIN where VOR = N× Vo.)*, set slightly greater than 1 (~1.05) at maximum load and maximum input voltage. The rest of the procedure will become clear shortly. See **Figure 1.7**. We can see that the 1.05 gain target ensures we are slightly to the left of the MoP! Not to the right. Ever, as we can show! We will automatically move to the left of  $f_{HI}$  if the input voltage falls. But if the output is, say, suddenly unloaded, the output will jump momentarily higher (above the set 1.05). The control loop will then try to reduce it by increasing the frequency, but won't need to go above  $f_{HI}$ , since even the no-load curve gain drops to below 1.05 near the MoP, which we know occurs at  $f_{HI}$ . It will thus all work just fine between two frequency extremes. But the key is to set the gain target (using the correct turns ratio in effect), to slightly above 1. Most LLC designers do so, but rather inadvertently.

As a side note, all WPT systems around us today actually ignore even the above simple guidance concerning the set gain target/desired VOR. We already know that all the "approved" Qi transmitters *turned a blind eye to the critical C/L ratio*, so the "power capability of an LC network" was not understood. But now we must recognize that all their "approved" receiver coils, have *different turns ratios with respect to even a single transmitter*, and also, the receivers are virtually allowed to set output voltages of their choice (no real guidelines to set Vo, and to thereby establish the desirable VOR, which we just learned should be set slightly higher than VINMAX).

In general, the gain target of any existing WPT technology out there could just end up being less than 1. Unknowingly! As a result, WPT systems doing "frequency modulation" will end up trying to control the output by operating to the *right* of "fHI" as indicated in **Figure 1.7**. Not strictly to its left as strongly recommended. One obvious drawback of that, besides higher (broader) EMI, is that at very light loads, the transmitter can no longer reduce the gain any further by raising the frequency, so the receiver has to suddenly apply an internal overvoltage clamp (usually dissipative), just to protect itself. Keep in mind that Qi restricts its operation between 115- 205 kHz, to simplify the design of the power stage. But if the control loop tries to increase the frequency above the upper limit of 205kHz, internal clamps are activated within the receiver to try and protect itself. Not elegant! A heavy price to pay for ignoring both power capability, and VOR.

Besides, a key question for any clamp is: for how long is it safe? Or even practical? That in fact, is one of the reasons Qi can never do laptops! Imagine applying typically 50-100 Watt Zener clamps inside the laptop, for over a second (for that is how long the correction loop of Qi can be in practice, with a few missed packets, as has been commonly observed). Now add to that mess the K-variability factor, and the double peaking issue arising from Cs, neither of which we have even considered while doing the gain plots in **Figure 1.7**, and all bets are off! Proprietary solutions are probably the only solution to these very complex issues and the unpredictable interplay of their influencers.

As we had declared initially: the awesome power and potential that resonance brings to our doorstep quite literally, comes with a hefty price tag: *it demands total design expertise*. It could have been corrected, but that window of opportunity has firmly closed. Only proprietary solutions exist to solve this issue (too).

## **LLC and the Power of Magnetics**

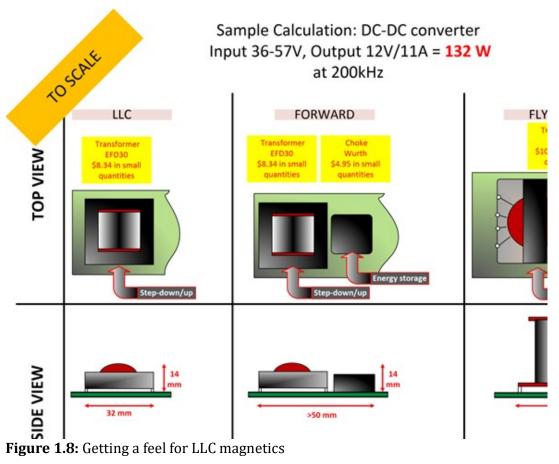

Before we reveal our design procedure, we try to get a final "feel" for the magnetics of resonant topologies, the LLC in particular, and why that is another big attraction to use the topology, compared to the magnetics in classical power conversion. A lot of what we will learn applies in principle to WPT systems too.

**Figure 1.8** provides a good visual impression of the key advantage: the lowered size (and cost) of LLC magnetics—making it akin to a Forward converter transformer in size, plus without the need for any output choke. Focusing on the transformer only for now, it is small, because no fraction of the useful power delivered to the load in an LLC topology, or in a Forward converter transformer, needs to be ever stored, even temporarily, within its magnetic core during the power transfer/conversion process. The reason is that the Secondary windings conduct at the very same time as the Primary windings, so the flux associated with the load current flowing in the Secondary, is fully canceled by the additional flow of current flowing into the Primary winding to support it. The input current component associated with the actual delivery of useful power to the Secondary, is obviously load-dependent. The magnetization, excitation component is not. The latter leads to the steady conduction loss term we discussed earlier, and the residual flux at all times within the transformer core. Since any flux attributable to the load-dependent currents flowing in the Primary and Secondary windings, cancel each other out, the net flux we are left with in the core is still, just the one related to the initial magnetization current component, which was and remains loadindependent. Think of the flux as the one present at zero load current. It doesn't budge with load! Nature opposes any change. And it has done so very successfully here! Fully! If a Forward converter transformer, or an LLC/WPT magnetic core, is made visibly larger for higher powers, it is really not to support higher load currents per se. It is made "bigger" only to accommodate the thicker copper windings constituting the Primary and Secondary (more window area, or larger surface area for better cooling). And for the same reason, the "core loss" term in a Forward converter's transformer or in an LLC or WPT system, is also just based on the zero-load-current case! Not for maximum load current. How convenient! If it gets hot, it is not core losses from within the core, just conduction losses from the adjacent copper, to consider and reduce.

To re-iterate: the transformer needs to store only the energy related to the *load-independent*, "magnetization current" component, which can be intuitively thought of as an excitation component necessary to initiate basic "transformer action", thanks to Faraday's law of magnetic induction. Nothing related to the actual power transfer process is stored in the core! So typically, in an LLC or Forward converter, the transformer volume requirement is roughly *half to one-third the size of a Flyback transformer of the same power capability*. In a Flyback transformer, the Secondary windings do *not* conduct at the same time as the Primary windings. So, we basically need to store, *all* the energy meant for delivery to the output, inside the transformer core, during the ON-time, then pull it *all* out during the OFF-time. The Flyback transformer core is thus a bit like an Amazon warehouse, for energy! It needs to be *big*. For the same reason too: everything that goes out, must be stored there at some point of its journey.

But the Forward converter, unlike the LLC, needs an output choke, to finally store a certain fraction of the load-dependent energy too. That is because energy storage in a magnetic core is fundamental to the power transfer process of all PWM-based classical power topologies. Though by different amounts. That aspect was discussed in detail in Chapter 5 of Switching Power Supplies A to Z, Second Edition, in particular on Page 208. Reproduced here partially:

$$\Delta\epsilon_{_{BUCK}} = \frac{P_{_{IN}}}{f} \times \left(1 - D\right); \; \Delta\epsilon_{_{BOOST}} = \frac{P_{_{IN}}}{f} \times \left(D\right); \; \Delta\epsilon_{_{BUCK-BOOST}} = \frac{P_{_{IN}}}{f}$$

This tells us how much energy per cycle needs to be "cycled/stored" for the three fundamental (classical) topologies. Since  $P_{IN}/f$ , is the energy per cycle, we learn that the Buck-Boost (or the Flyback) need to temporarily store (and then release) 100% of the energy making its way to the output. In comparison, Buck inductors tend to be small, especially when the amount of "bucking (stepping-down)" asked of them, is less. And why Flyback (Buck-Boost) magnetics are so much bigger.

Basically, in the case of the Flyback topology, its transformer is its energy-storage element too, besides providing "transformer action" (voltage scaling and isolation in particular). It needs to temporarily store 100% of the energy transferred (not any fraction of the duty cycle, D), since a Flyback is just a Buck-Boost derivative. Similarly, a Forward converter, despite a simple transformer, *does* need an output choke, since it is a Buck-derived topology, and therefore needs to store a certain fraction (proportional to 1-D) of the power transferred. All initial points are in perspective by now, hopefully providing us a much better "feel" for resonance. So, we will now get deep into the simplified but accurate design procedure suitable for any LLC and (correctly designed, i.e. *no Cs*) WPT system.

## **Defining the Kernel**

As indicated, we just need to take a kernel, study it very well, and then use scaling laws to take it to any power, frequency and input voltage level. But we also want to introduce a factor for establishing a certain gain margin to serve us well when the input voltage starts to droop, i.e. to handle input variations! A lot of that was already demonstrated in Switching Power Supply, Design and Optimization, Second Edition, but the following key items, were not considered, which we want to do here:

- a) How to scale as per input voltages. In other words, if the kernel was studied for an input DC range of 32V to 52V input, and now we want our LLC converter to work from 200V to 400V DC. How does that affect our overall scaling of components?

- b) How to handle different coupling coefficients? In the previous exercise, we had a fixed K of 0.9 and when we scaled, we kept the same K. In reality, we want to consider any K, even very low couplings, as in WPT.

In our previous exercise we had initially started off with a certain very low frequency kernel, and then scaled that to become a 25.5W LLC converter for a Power over Ethernet (PoE) application (32V to 52V DC input). So just for historical continuity, we have for the graphical aids presented herein, used the same values of  $L_P$  and  $C_P$  (57.2 $\mu$ H and 225.8 $\mu$ F) that we had arrived at, as a result of scaling our very first very low-frequency kernel. Now, we will just use these suggested PoE converter values as the kernel for the next scaling exercise here. Since we are scaling anyway, we could use any initial kernel. So, we then introduced these  $L_P$  and  $C_P$  values into a general Mathcad spreadsheet to generate the graphical aids presented. The spreadheet is in the Appendix to Chapter 1.

Just to throw more light on the gain curves we will get in an LLC topology, as an intermediate step, we used the above Mathcad spreadsheet to suggest the "recommended" load resistor of 20.6 ohms. And then we used multiples, or fractions, of that to generate the stacked gain plots in **Figure 1.9**. Note that 20.6 ohms is the equivalent AC load resistor to be applied to the equivalent AC-AC, non-isolated model shown in **Figure 1.5c**. It was recommended by the spreadsheet, to be able to deliver the desired average power of 25.5 Watts in the final converter, over the desired input range of 32 to 52 VDC.

We have also used Mathcad to predict exactly where the entire LC network appears "inductive" (solid lines) and where it appears "capacitive" (dashed/dotted lines). It tells us where ZVS will occur and where it won't! A bit to our initial surprise we do see that the changeover from solid to dotted does not occur precisely at the "peak" value, as always somehow assumed. The reason is that the peak is determined where the leakage  $(1-K)\times L_P$  and resonant capacitor  $C_P$ , are in perfect resonance ("dead short")... but on closer examination, that does not necessarily coincide exactly where the entire network (including  $L_P \times (K)$ ) "resonates". Basically there is a slight shift on account of the magnetizing inductance and the load entering into the picture. The practical implication of that is it may not be enough to be merely "slightly to the right" of the peak voltage for ensuring ZVS. Maybe a little more than "slightly"! But in any case, the transition from lossless to lossy switching is a bit gradual anyway, so though the losses may go up slightly as we leave the solid region of the curves, and enter the dotted portion (on our way to the peak), they might still be acceptable enough, to *not* warrant more effort on our part to tweak the control algorithm.

In the lower part of **Figure 1.9**, we also show the complete mess the mere introduction of a reflected capacitance of 100nF (arbitrarily chosen), from the Secondary to the Primary side, causes. *On display here is all what is wrong with modern WPT*: the "double resonator" flaw we had talked a lot about! Notice there are two peaks, behaving differently. The one which shifted to the right, has an even more dramatic shift than anticipated without  $C_S$ . So in the case of  $Q_I$ , a good question to also ask is: what if the resonant peak has not just moved to "141kHz", as we often say as a ballpark estimate of the shifting, but actually to above 205kHz, (the upper operating limit of  $Q_I$ )? How can we even ever hope to regulate? We are stuck on the wrong (left) side of the resonant curve. If we lower the frequency, the gain collapses further! And of course we are not in a region where ZVS will occur. Unless the "double resonator flaw" helps us inadvertently in this case. Because we have another peak with  $C_S$  present. This has actually shifted to the left of the no-load peak location  $f_{LO}$ . Very hard to ever predict how any control loop will react to all this mess. Most likely, a bunch of "mysterious turn-offs". And then: "inherently poor user experience of inductive systems".

Let us move on, without Cs here-ever-after!

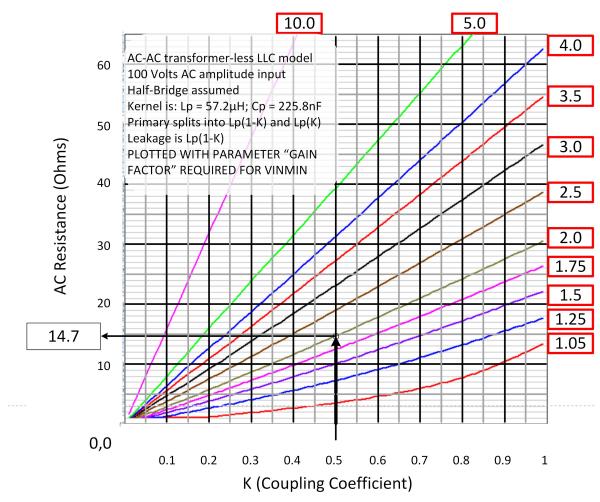

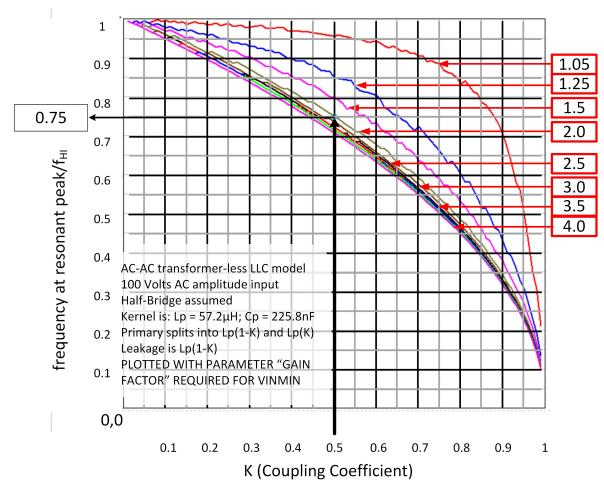

## Practical Design Example of a wide-input 900W LLC/WPTconverter

With the above kernel, we have generated two key design curves, shown in **Figure 1.10**, and **Figure 1.11**. Keep in mind that the values used were  $L_P = 57.2 \mu H$  and  $C_P = 225.8 nF$ . So, here is the challenge: we want to deliver 900W into a 48V output. Select the best L and C values for the converter for an estimated coupling of K = 0.5. For EMI compliance reasons, we want to stay below 150kHz guaranteed. What are the best operating frequencies to carry out meaningful simulations, to test its performance? We are assuming an input DC varying from 200 to 400V.

On account of the high-power the obvious choice is a full bridge, not a half bridge. At 400VDC therefore, the equivalent AC wave applied to the input of the resonant network is as per FHA:

$$V_{INMAX\_AC} = V_{INMAX\_DC} \times \frac{4}{\pi}$$

Volts

$$V_{INMAX\_AC} = 400 \times \frac{4}{\pi} = 509.3 \text{ Volts}$$

This is the equivalent amplitude of the sine-wave applied as per FHA. (For a half bridge we would have divided this by 2).

From **Figure 1.10**, For a coupling of 0.5 and a V<sub>INMAX</sub>/V<sub>INMIN</sub> ratio ("gain factor") of 2 (to allow us to reach 200VDC from the original 400VDC), we see that the recommended resistor to be placed on the output of our non-isolated AC-AC equivalent circuit of **Figure 1.5c**, is 14.7 ohms.

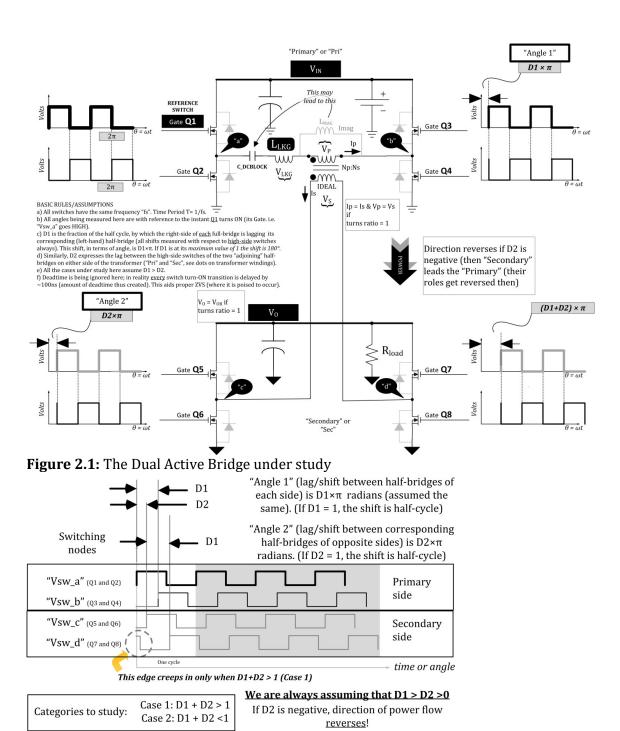

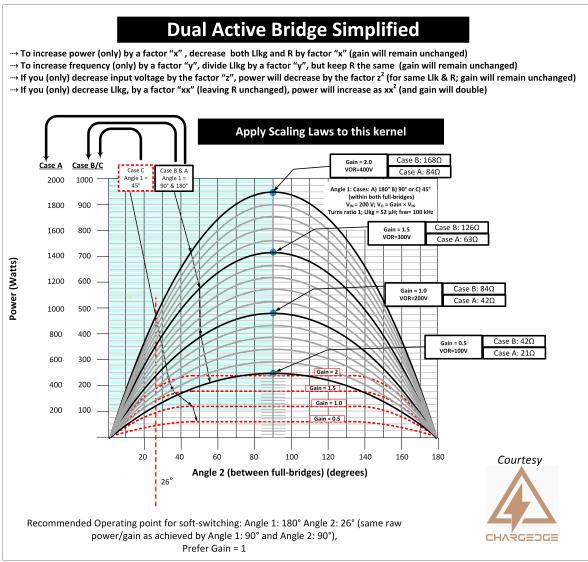

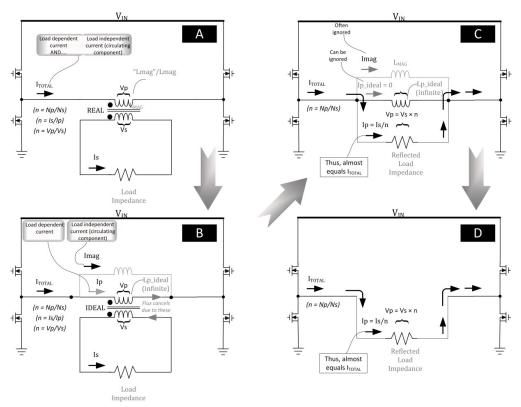

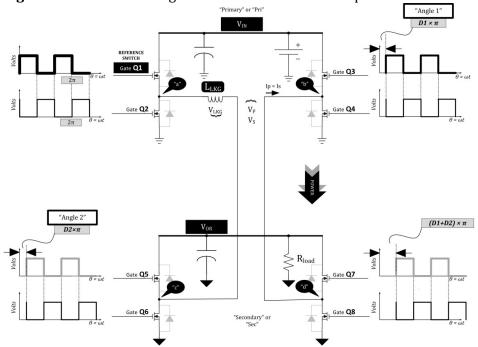

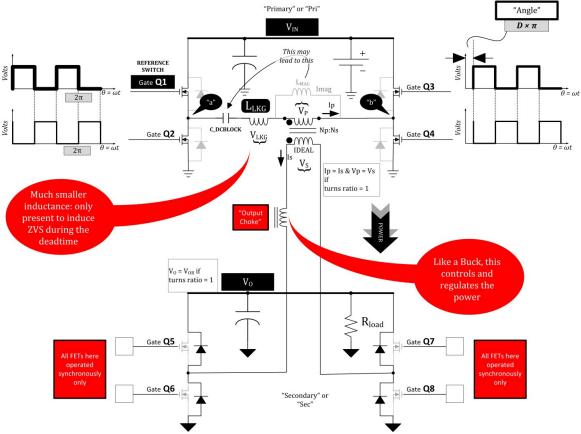

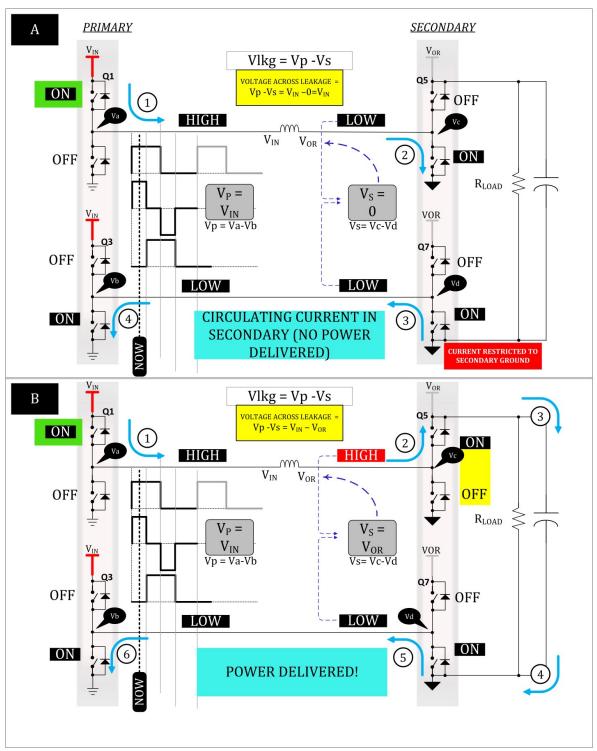

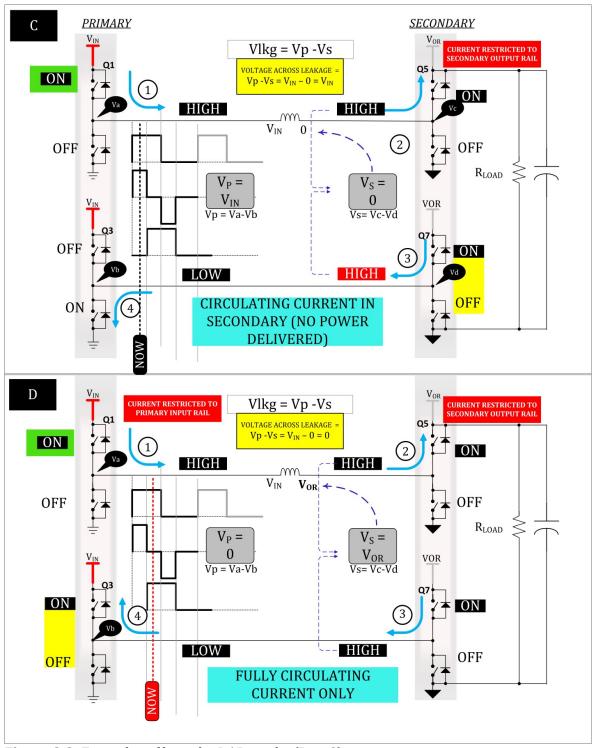

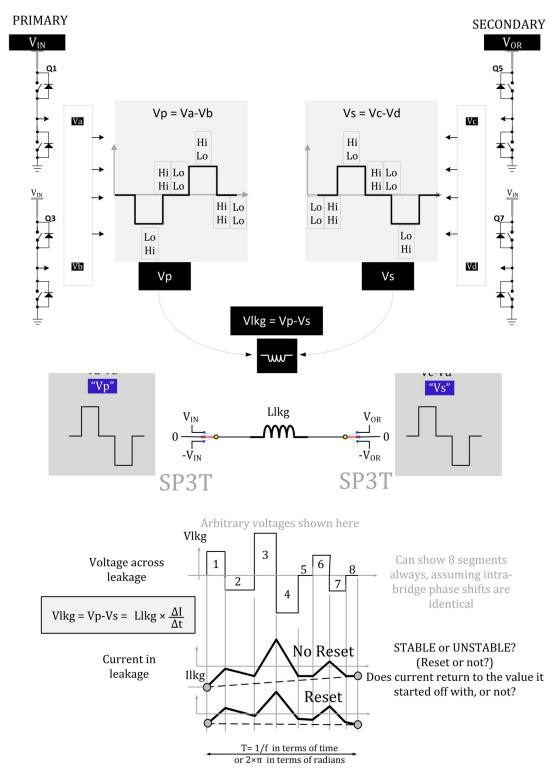

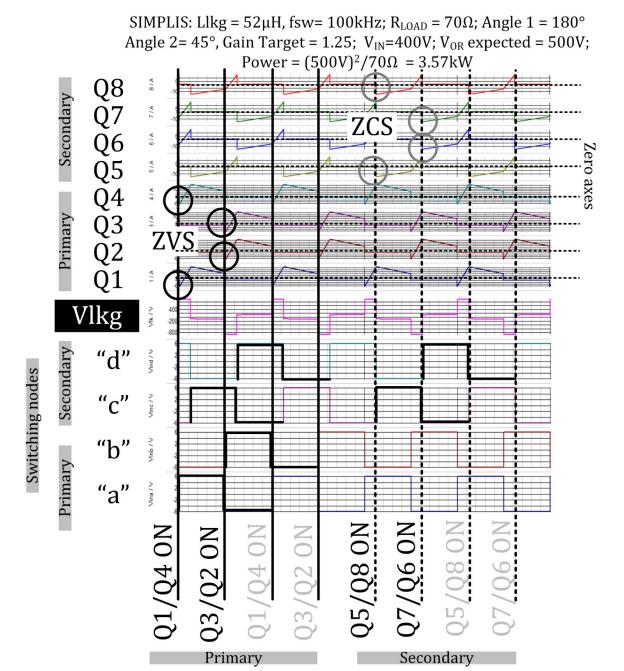

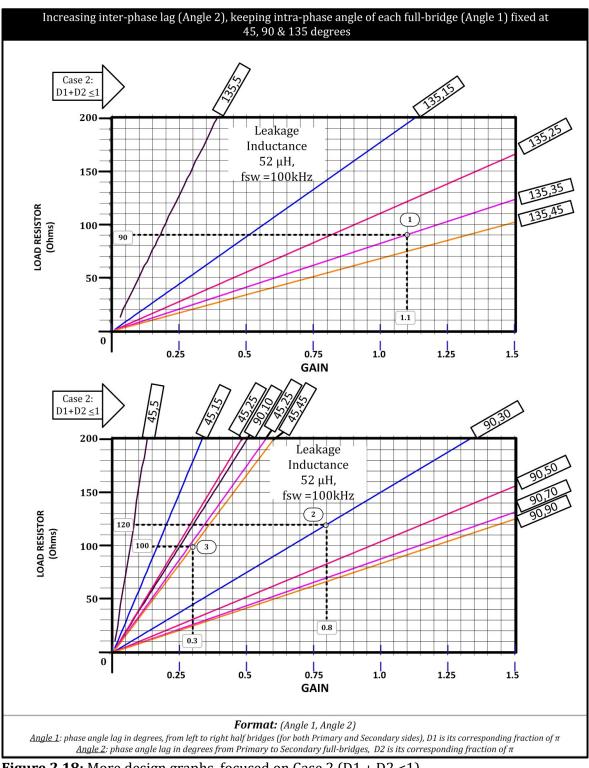

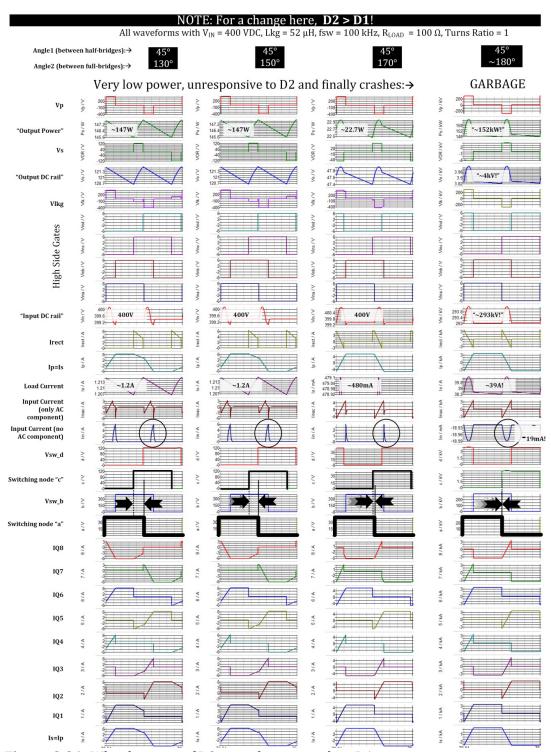

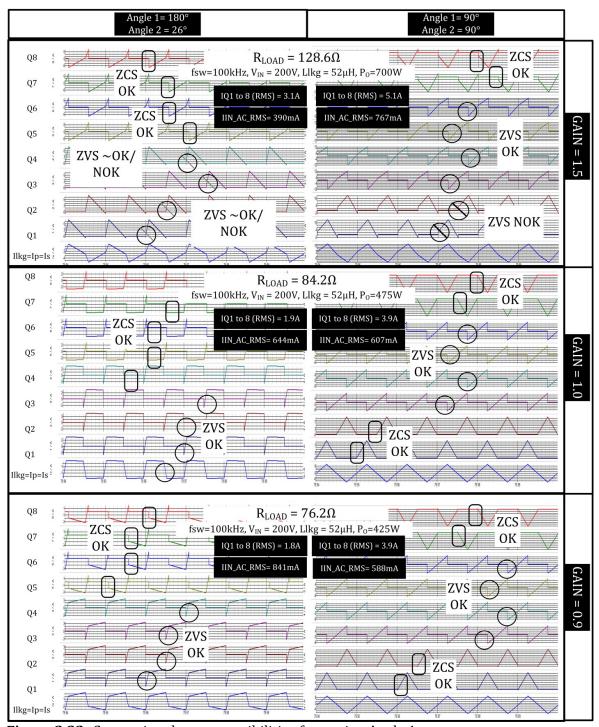

This load resistor is actually valid, *irrespective of the applied/assumed input actually*, because it produces just the right amount of "bulge" in the gain profile curve, in conjunction with the selected C and L (the C/L ratio in effect), to allow for a Gain of 2, occurring somewhere between f<sub>HI</sub> and f<sub>LO</sub>, before the gain curve rolls off! So, that there is no hint of overdesign either! Just the right "bulge" in the resonance curve.